2025 Электротехника, информационные технологии, системы управления № 54

Научная статья

DOI: 10.15593/2224-9397/2025.2.12

УДК 004.89

#### М.С. Никитин

Пермский национальный исследовательский политехнический университет, Пермь, Российская Федерация

### АЛГОРИТМ СИНТЕЗА ТРАНЗИСТОРНОЙ СХЕМЫ С МНОГОВАРИАНТНЫМ РЕЗЕРВИРОВАНИЕМ

Одним из перспективных методов обеспечения надежности цифровой аппаратуры является комбинированное или гибридное резервирование. При этом находится наиболее предпочтительный вариант, сочетающий различные известные виды резервирования: дублирование, троирование (мажоритирование), глубокое мажоритирование, скользящее резервирование и др. Прогресс интегральных технологий позволяет выполнять резервирование на наноуровне каждого отдельного транзистора, что является на настоящий момент «крайней» степенью резервирования, хотя уже и сегодня используются транзисторы с несколькими затворами, что также может считаться резервированием. Тем не менее особенности комплексирования резервирования на уровне транзисторов вместе с другими видами резервирования в настоящий момент исследованы не в полной мере. Вместе с тем увеличение степени избыточности на этом уровне наталкивается на фундаментальные ограничения в количестве последовательно соединенных транзисторов. Но есть информация по снижению этих ограничений в будущем на основе новых материалов при формировании транзисторов. Важным направлением повышение надежности является снижение потребляемой мощности при ограничениях на временную задержку для заданной степени избыточности. В статье рассматривается обеспечение надежности с учетом формирования различных вариантов избыточности, характеризуемых одинаковой вероятностью безотказной работы, но различными показателями потребляемой мощности и временной задержки, которые, как оказалось, зависят от формы представления соответствующей логической функции при создании топологии резервированной схемы. Целью исследования является разработка алгоритма синтеза транзисторной схемы с многовариантным резервированием по заданной степени избыточности. Методы исследования базируются на научно-методическом аппарате теории надежности, теории алгоритмов и программирования. В результате исследования разработаны алгоритм и программа синтеза транзисторной схемы с многовариантным резервированием. Практическая значимость: разработанный алгоритм и программа позволяют автоматически формировать транзисторные структуры с многовариантным резервированием, что обеспечивает выбор наиболее предпочтительного варианта.

**Ключевые слова:** отказоустойчивость, транзистор, избыточность, расчетверение, алгоритм.

#### M.S. Nikitin

Perm National Research Polytechnic University, Perm, Russian Federation

# MULTI-OPTIONAL REDUNDANCY TRANSISTOR CIRCUIT DESIGN ALGORITHM

One of the promising methods of ensuring the reliability of digital equipment is combined or hybrid redundancy. In this case, the most preferable option is found, combining various known types of redundancy: duplication, tripling (majoritation), deep tripling, sliding redundancy, etc. The progress of integrated technologies allows for redundancy at the nanolevel of each individual transistor, which is currently the "extreme" degree of redundancy, although transistors with several gates are already used today, which can also be considered redundancy. Nevertheless, the features of combining redundancy at the transistor level with other types of redundancy have not yet been fully studied. At the same time, increasing the degree of redundancy at this level encounters fundamental limitations in the number of series-connected transistors. But there is information on reducing these limitations in the future based on new materials when forming transistors. An important direction for increasing reliability is reducing the power consumption with restrictions on the time delay for a given degree of redundancy. The article considers ensuring reliability taking into account the formation of various redundancy options characterized by the same probability of failure-free operation, but different indicators of power consumption and time delay, which, as it turned out, depend on the form of representation of the corresponding logical function when creating the topology of the redundant circuit. The aim of the study is the development of an algorithm for synthesizing a transistor circuit with multivariant redundancy according to a given degree of redundancy. The research methods are based on the scientific and methodological apparatus of reliability theory, theory of algorithms and art of the programming. As a result of the study an algorithm and program for synthesizing a transistor circuit with multi-variant redundancy have been developed. Discussion: designed algorithm and program allow for the automatic formation of transistor structures with multi-variant redundancy, which ensures the selection of the most preferable option.

**Keywords:** Fault Tolerant, Transistor, Redundancy, Fourfold Redundancy, Algorithm.

#### Введение

Повышение надежности, отказо- и сбоеустойчивости вычислительных систем и их элементов является важнейшей задачей обеспечения качества интегральных микросхем [1–3]. Помимо обычных отказов и сбоев в классических моделях отказов [4, 5] речь может идти также и о радиационных явлениях [6], а также и о не только природных воздействиях — о намеренных дестабилизирующих воздействиях. Для обеспечения надежности используется пассивная и активная отказо и сбоеустойчивость [7], например, троирование (мажоритирование) [8], парирующее отказ или сбой в одном из трех идентичных каналов. Большее число сбоев и отказов парируется при глубоком мажоритировании [9]. Обеспечение надежности програмируемых логических интегральных схем (ПЛИС) [10] имеет особое значение, так как они в настоящее время содержат десятки миллиардов транзисторов, десят-

ки миллионов логических элементов, коммутаторов межсоединений и ячеек конфигурационной памяти, количество выводов (pin), «ножек» микросхем достигло размерности сотен и даже тысячи. Поэтому возрастает интерес к транзисторному уровню резервирования в рамках тренда своего рода увеличения глубины избыточности до наноразмеров [11–14]. На этом уровне возникают новые возможности получения различных вариантов избыточности [15], например, отличающихся по потребляемой мощности, а ее снижение, в свою очередь, является другим важнейшим фактором и направлением так называемых «зеленых» вычислений [16, 17]. С другой стороны, имеются ограничения Мида-Конвей [18] на количество подряд следующих транзисторов в цепи, которое равно четырем, обусловленное падением напряжения «истоксток», однако в ПЛИС оно снижено до трех, что требует определенной декомпозиции схем, в которых применяется транзисторное резервирование. Все эти факторы с учетом использования скользящего резервирования и других вариантов [19, 20] и диагностирования [21], а также применяемого распределения Вейбулла [22] требуют разработки средств расчета, формирования вариантов и выбора предпочтительного варианта.

**Целью представленной работы** является разработка алгоритма синтеза транзисторной схемы с многовариантным резервированием по заданной степени избыточности в рамках метода многовариантного резервирования с учетом особенностей логико-топологической избыточности.

## 1. Расчет надежности цифровых схем, использующих многовариантное резервирование

При расчете надежности комбинируются формулы существующих основных методов обеспечения надежности, таких как мажоритирование  $P_{>=n,\Gamma,M}$ , резервирование на транзисторном уровне  $P_{TrR}$ , дублирование D, скользящее резервирование  $P_{sb}$  (основные элементы q и резервные g) [19, 20].

При этом необходим дополнительно контроллер диагностики и восстановления  $P_{dr}$ . В качестве параметров используется время работы t, интенсивность отказов  $\lambda$ , количество транзисторов L, потребляемая мощность W, временная задержка T, площадь кристалла S. Получаем выражение:

$$P_{\geq n}(t, \lambda_{\geq n}, W_{\geq n}, T_{\max \geq n}, S_{\geq n}, L_{\geq n};$$

$$P_{\geq n.\Gamma M}(t, \lambda_{\geq n.\Gamma M}, W_{\geq n.\Gamma M}, T_{\max \geq n.\Gamma M}, S_{\geq n.\Gamma M}, L_{\geq n.\Gamma M};$$

$$P_{(r+1)^{2}TrR}(t, \lambda_{\geq n.TrR}, W_{\geq n.TrR}, T_{\max \geq n.TrR}, S_{\geq n.TrR}, L_{\geq n.TrR}^{*};$$

$$P_{sb}(q, g, t) = \sum_{i=n}^{q+g} C_{q+g}^{i} \cdot e^{-i\lambda t^{\alpha}} \cdot [1 - e^{-\lambda t^{\alpha}}]^{q+g-i} P_{dr}(t);$$

$$D(t, \lambda_{D(t)}, W_{D(t)}, T_{D(t)}, S_{D(t)}, L_{D(t)}).$$

(1)

Задача заключается:

I) в максимизации вероятности безотказной (бессбойной) работы P и/или достоверности функционирования D(t) при заданных ограничениях на произведение потребляемой мощности на временную задержку  $W^*T(S,L)$ :

I)

$$P_{\geq n}(t, \lambda_{\geq n}, W_{\geq n}, T_{\max \geq n}, S_{\geq n}, L_{\geq n} \times P_{\geq n, \Gamma_{\mathbf{M}}}(t, \lambda_{\geq n, \Gamma_{\mathbf{M}}}, W_{\geq n, \Gamma_{\mathbf{M}}}, T_{\max \geq n, \Gamma_{\mathbf{M}}}, S_{\geq n, \Gamma_{\mathbf{M}}}, L_{\geq n, \Gamma_{\mathbf{M}}} \times P_{(r+1)^{2}TrR}(t, \lambda_{TrR}, W_{TrR}, T_{\max TrR}, S_{TrR}, L_{TrR} \times P_{sb}(q, g, t) = \sum_{i=n}^{q+g} C_{q+g}^{i} \cdot e^{-i\lambda t^{\alpha}} \cdot [1 - e^{-i\lambda t^{\alpha}}]^{q+g-i} P_{dr}(t) \times P_{sb}(t, \lambda_{D(t)}, W_{D(t)}, T_{\max D(t)}, S_{D(t)}, L_{D(t)}) \rightarrow \max$$

$$(2)$$

при

$$W \cdot T \leq (W \cdot T)_{\text{треб}} \& (S \leq S_{\text{треб}}) \& (L \leq L_{\text{треб}});$$

II) в минимизации  $W^*$  T, при заданных ограничениях S, L, P и/или достоверности функционирования D(t) при обычном дублировании:

II)

$$W \cdot T \rightarrow \min$$

при

$$P_{\geq n}(t, \lambda_{\geq n}, W_{\geq n}, T_{\max \geq n}, S_{\geq n}, L_{\geq n} \times \times P_{\geq n.\text{TM}}(t, \lambda_{\geq n.\text{TM}}, W_{\geq n.\text{TM}}, T_{\max \geq n.\text{TM}}, S_{\geq n.\text{TM}}, L_{\geq n.\text{TM}} \times \times P_{(r+1)^{2}TrR}(t, \lambda_{TrR}, W_{TrR}, T_{\max TrR}, S_{TrR}, L_{TrR} \times \times P_{sb}(q, g, t) = \sum_{i=n}^{q+g} C_{q+g}^{i} \cdot e^{-i\lambda t^{\alpha}} \cdot [1 - e^{-i\lambda t^{\alpha}}]^{q+g-i} P_{dr}(t) \times \times D(t, \lambda_{D(t)}, W_{D(t)}, T_{\max D(t)}, S_{D(t)}, L_{D(t)}) \leq \times P_{\text{TDE 6}} \& (S \leq S_{\text{TDE 6}}) \& (L \leq L_{\text{TDE 6}}).$$

$$(3)$$

При этом для поиска наиболее предпочтительного варианта транзисторного резервирования (структурной схеме надежности [23]) по заданному r, которое означает количество парируемых отказов (сбоев) в транзисторной структуре, получают эквивалентные в смысле парирования отказов (сбоев) логические выражения в дизъюнктивной нормальной форме (ДНФ), конъюнктивной нормальной форме (КНФ) и в смешанных формах, а по заданному количеству транзисторов v получают множество логико-топологических комбинаций трех вариантов:

$$F:\{\{f_{\nu,\text{ДН}\Phi}{}^{r}\}\{f_{\nu,\text{КН}\Phi}{}^{r}\},\{f_{\nu,\text{КОМ}\bar{6}}{}^{r=\alpha+\beta}\}\Longrightarrow$$

$$\left(\prod_{\xi=1}^{e_{\xi}}P_{(r+1)^{2}}(t,\lambda_{\xi,TrR})_{\xi,TrR}\cdot\prod_{\vartheta=1}^{e_{\xi}}P_{n,r,\text{M},m_{\vartheta}}^{*}(\lambda_{\vartheta},\lambda_{TrR.\vartheta})\cdot\prod_{\omega=1}^{e_{\omega}}P_{n,m_{\omega}}^{*}(\lambda_{\omega},\lambda_{TrR.\omega})\right)_{\text{ДОГ-ТОПОЛ}}.$$

$$W_{\xi},W_{\vartheta},W_{\overline{\omega}};T_{\xi},T_{\vartheta},T_{\overline{\omega}};S_{\xi},S_{\vartheta},S_{\overline{\omega}};L_{\xi},L_{\vartheta},L_{\overline{\omega}}$$

По полученному F осуществляют схемотехническое и топологическое моделирования, к примеру, в системах топологического моделирования, например, Microwind [24]. По его результатам выбирают предпочтительный вариант транзисторного резервирования:

$$\prod_{\xi=1}^{e_{\xi}} P_{(r+1)^2}(t, \lambda_{\xi.TrR})_{\xi.TrR}.$$

(5)

#### 2. Комбинирование вариантов и построение множества Парето

Далее путем комбинирования  $e_{\xi}, e_{\vartheta}, e_{\omega}$  и увеличения резервирования — параметров n, r получают множества Y реализаций:

$$\left\{ \left( \prod_{\xi=1}^{e_{\xi}} P_{(r+1)^{2}}(t, \lambda_{\xi, TrR})_{\xi, TrR} \cdot \prod_{9=1}^{e_{\xi}} P_{n, r, M, m_{9}}^{*}(\lambda_{9}, \lambda_{TrR, 9}) \cdot \prod_{\omega=1}^{e_{\omega}} P_{n, m_{\omega}}^{*}(\lambda_{\omega}, \lambda_{TrR, \omega}) \right)_{\text{MOF-TOHON}} \right\}_{y_{\psi}} \in Y.$$

$$(6)$$

$$y_{\psi} \in Y.$$

По Y получают Парето-оптимальные варианты [25]  $Y_{Par}$ . Например, по некоторым двум условным параметрам это может быть описано выражением:

$$Y_{Par} = y_{\psi} \cup y_{\gamma} : \forall \psi \forall \gamma [y_{\psi}(P_{\psi}\Omega_{\psi}), y_{\gamma}(P_{\gamma,\gamma}\Omega_{\gamma})] \&$$

$$[(P_{\psi} = P_{\gamma})(\Omega_{\psi} > \Omega_{\gamma}) \vee (P_{\psi} > P_{\gamma})(\Omega_{\psi} = \Omega_{\gamma})] = falce,$$

(7)

где

$$(P_{\mathsf{W}} = P_{\mathsf{y}})(\Omega_{\mathsf{W}} > \Omega_{\mathsf{y}}) \vee (P_{\mathsf{W}} > P_{\mathsf{y}})(\Omega_{\mathsf{W}} = \Omega_{\mathsf{y}}) \tag{8}$$

условие сравнимости двух условных параметров P и  $\Omega$ .

В случае сравнимости остается только один вариант:

$$\begin{split} Y_{Par} &= y_{\psi} : \forall \psi \forall \gamma [y_{\psi}(P_{\psi}\Omega_{\psi}), y_{\gamma}(P_{\gamma,\gamma}\Omega_{\gamma})] \& \\ & \overline{(P_{\psi} = P_{\gamma})(\Omega_{\psi} > \Omega_{\gamma}) \vee (P_{\psi} > P_{\gamma})(\Omega_{\psi} = \Omega_{\gamma})]} = true \Big) \& \\ & (P_{\psi} > P_{\gamma})(\Omega_{\psi} = \Omega_{\gamma}); \\ & Y_{Par} &= y_{\gamma} : \forall \psi \forall \gamma [y_{\psi}(P_{\psi}\Omega_{\psi}), y_{\gamma}(P_{\gamma,\gamma}\Omega_{\gamma})] \& \\ & \overline{(P_{\psi} = P_{\gamma})(\Omega_{\psi} > \Omega_{\gamma}) \vee (P_{\psi} > P_{\gamma})(\Omega_{\psi} = \Omega_{\gamma})]} = true \Big) \& \\ & (P_{\psi} = P_{\gamma})(\Omega_{\psi} > \Omega_{\gamma}). \end{split}$$

Формирование вариантов с одинаковыми параметрами представляется маловероятным, однако они тоже включаются во множество  $Y_{Par}$ , тем более что целесообразно учесть дополнительные параметры, например, число линий связи, аппаратурные затраты на источники электропитания, стоимостные оценки и пр., кроме того, возможно, некоторые параметры могут быть получены при моделировании, например, качественные показатели форм сигналов и др. Возможно формирование сообщения о неподчиненности (несравнимости) всех вариантов (все множество вариантов — множество Парето  $Y_{Par}$ ). Из множества Парето  $Y_{Par}$  выбирают заданный оптимальный вариант с заданными ограничениями. Иначе опять увеличивают резервы.

Оптимизация выполняется по результатам поиска наиболее предпочтительных вариантов с учетом логико-топологических характеристик отдельных элементов (устройств) и комплексирования различных методов для группы (системы) из элементов (устройств). При этом рассматриваются и варианты гибридного резервирования и используются градиентные и эволюционные известные методы. Эта оптимизация может быть выполнена известными методами, например, обобщенного приведенного градиента или эволюционным (Evolutionary algorithm – EA, Genetic algorithm) [25, 26]. Возможно также использование алгоритма имитации отжига (Simulated annealing) [26].

#### 3. Автоматический синтез резервированных структур

С целью формирования вариантов F (3) транзисторного резервирования разработан алгоритм, позволяющий комбинировать не только формы КНФ и ДНФ, но и смешанные формы. Основные варианты резервированных схем транзистора (КНФ и ДНФ), которые можно обозначить как  $\mathrm{IO}(r+1)=2^r$ , комбинаторно являются так называемыми композициями целого числа, например, для r=1 их два, для r=2 их четыре, для r=3 их восемь.

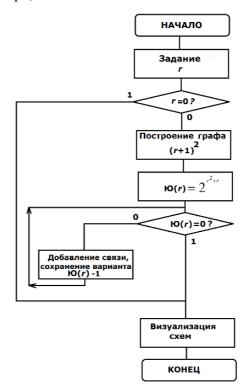

Рис. 1. Схема алгоритма формирования вариантов транзисторного резервирования

Для учета смешанных вариантов предлагается взять за основу ДНФ и методом перебора формировать новые связи, включая дополнительные, учитывающие «кольцевые» пути. При этом формируется регулярный граф, в котором вершины являются транзисторами, всего (r+1)2 вершин — транзисторов, а ребра — связи между ними. Вершина структурированы в виде r+1 ветви.

Работа алгоритма заключается в формировании такого графа и комбинаторном добавлении новых связей, при этом допускаются только связи «по столбцу», перекрестные связи не рассматриваются. Схема алгоритма формирования вариантов транзисторного резервирования представлена на рис. 1.

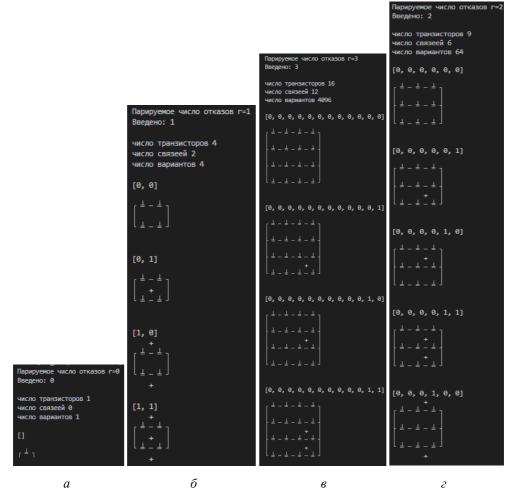

Программа разработана на языке Python. Примеры формирования вариантов графов для r=0 (без резервирования), r=1, r=2 и r=3 показаны на рис. 2. На рис. 2 «кольцевая» связь показана «+», например, вариантом 0,0,0,1,0,0 для r=2 ( $\epsilon$ ). Всего имеется 64 варианта, из них показано 5.

Рис. 2. Примеры формирования вариантов графов для r = 0. Новые связи обозначены символом «+»: a - r = 0;  $\delta - r = 1$ ; e - r = 2; z - r = 3

#### Заключение

Научная значимость исследования заключается в том, что предложены новые процедуры формирования структур многовариантного резервирования, включающего как известные методы, так и новые, например, транзисторное резервирование только наиболее важных устройств и элементов, поскольку избыточность такого резервирования очень высокая.

При этом для оценки эффективности автоматически формируются смешанные варианты, помимо КНФ и ДНФ, причем предложенный алгоритм строит соответствующий граф по ДНФ, в который итеративно добавляются необходимые связи. По существу, формируется Булеан множества связей по заданной степени избыточности.

Практическая новизна в том, что получен новый инструмент, позволяющий проектировщикам автоматически получать варианты резервирования.

Дальнейшие исследования могут быть направлены на разработку средств импортирования полученной схемы в системы топологического моделирования, например, Microwind [24]. В перспективе возможна разработка ПО для автоматической оценки топологий.

#### Библиографический список

- 1. ГОСТ 27.002–2015. Надежность в технике Основные понятия. Термины и определения. М.: Стандартинформ, 2016. 23 с.

- 2. ГОСТ 20911-89. Техническая диагностика. Термины и определения. М.: Стандартинформ, 2009. 11 с.

- 3. Надежность и эффективность в технике. Справочник в десяти томах / В.С. Авдуевский, И.В. Апполонов, Е.Ю. Барзилович [и др.]. V.S. Avduevskii (editor) // Reliability and efficiency in engineering. Handbook in 10 volumes. (In Russian). 1990. Т. 1–10. 3092 с.

- 4. Stuck-At Fault [Электронный ресурс]. URL: https://web.stanford.edu/class/ee386/public/stuck\_at\_fault\_6per\_page.pdf (дата обращения: 21.12.2024).

- 5. DFT Tutorial, Part 1 [Электронный ресурс]. URL: https://www.eecg.utoronto.ca/~ece1767/notes/lect2.pdf (дата обращения: 21.12.2024).

- 6. Максименко, С.Л. Анализ проблемы построения радиационностойких информационно-управляющих систем / С.Л. Максименко, В.Ф. Мелехин, А.С. Филиппов // Информационно-управляющие системы. -2012. -№ 2 (57). C. 18–25.

- 7. Error detection or correction of the data by redundancy in hardware (epo) patents (Class 714/E11.054) [Электронный ресурс]. URL: https://patents.justia.com/patents-by-us-classification/714/E11.054 (дата обращения: 12.01.2021).

- 8. Carmichael, C. Triple module redundancy design techniques for virtex FPGAs [Электронный ресурс] / C. Carmichael. URL: https://www.xilinx.com/support/documentation/application\_notes/xapp197.pdf (дата обращения: 12.01.2021).

- 9. Tyurin, S.F. Quadding against tripling & deep tripling / S.F. Tyurin // Journal of Applied Mathematics and Computation. 2018. DOI: 10.26855/jamc.2018.06.001

- 10. Tyurin, S.A. A Decoder Look up tables for FPGAs / S.F. Tyurin, R.V. Vikhorev // International Journal of Computing. 2021. Vol. 20, iss. 3. P. 365–373. DOI: 10.47839/ijc.20.3.2282

- 11. Tyurin, S.F. Retention of functional completeness of Boolean functions under "failures" of the arguments / S.F. Tyurin // Automation and Remote Control. 1999. Vol. 60. № 9, part 2. P. 1360–1367.

- 12. Transistor-level defect tolerant digital system design at the nanoscale [Электронный ресурс]. URL: https://www.researchgate.net/publication/237273805\_Transistor-Level\_Defect\_Tolerant\_Digital\_System\_Design\_at\_the\_Nanoscale (дата обращения: 12.12.2024).

- 13. El-Maleh Aiman, H. Transistor-Level Defect Tolerant Digital System Design at the Nanoscale [Электронный ресурс] / Aiman H. El-Maleh, Ahmad Al-Yamani and Bashir M. Al-Hashimi. URL: https://www.researchgate.net/publication/237273805\_Transistor-Level\_Defect\_Tolerant\_Digital\_System\_Design\_at\_the\_Nanoscale (дата обращения: 23.12.2024).

- 14. Tyurin, S.F. Hyper redundancy for super reliable FPGAs [Электронный ресурс] / S.F. Tyurin // Radioelectronic and computer systems. 2021. № 1. P. 119—132 URL: http://nti.khai.edu/ojs/index.php/reks/article/view/reks.2021.1.11/1449 (дата обращения: 04.07.2024).

- 15. Никитин, М.С. Топологические особенности транзисторного резервирования элементов ПЛИС / М.С. Никитин, С.Ф. Тюрин // Наноиндустрия. -2022. T. 15. № S8-1 (113). C. 160–163.

- 16. Tyurin, S. Green logic: models, methods, algorithms / S. Tyurin, A. Kamenskih // Green IT Engineering: Concepts, Models, Complex Systems Architectures. Eds: Kharchenko Vyacheslav, Kondratenko Yuriy, Kacprzyk Janusz. 2016. P. 69–86. DOI: 10.1007/978-3-319-44162-7

- 17. Tyurin S. Green Logic: Green LUT FPGA Concepts, Models and Evaluations // Green IT Engineering: Concepts, Models, Complex Systems Architectures, Studies in Systems, Decision and Control, V. Kharchenko, Y. Kondratenko, J. Kacprzyk (Eds.). XIV. 355 p. 147 illus. Berlin, Heidelberg: Springer International Publishing. 2017. P. 241–261. DOI: 10.1007/978-3-319-44162-7\_4

- 18. Mead, C.A. Introduction to VLSI Systems [Электронный ресурс] / C.A. Mead, L. Conway. URL: https://www.researchgate.net/publication/234388249\_Introduction\_to\_VLSI\_systems (дата обращения: 12.07.2023).

- 19. Tyurin, S.F. LUT's Sliding Backup / S.F. Tyurin // IEEE transactions on device and materials reliability. March 2019. Vol. 19, iss. 1. P. 221–225. DOI: 10.1109/TDMR.2019.2898724

- 20. Tyurin, S.F. A Quad CMOS gates checking method / S.F. Tyurin // International Journal of Computing. 2019. Vol. 18, iss. 3. P. 258–264.

- 21. Tyurin, S.F. Investigation of a hybrid redundancy in the faulttolerant systems / S.F. Tyurin // Radio electronics computer science control. 2019. Iss. 2. P. 15–22. DOI: 10.15588/1607-3274-2019-2-3

- 22. Weibull, W.A statistical distribution function of wide applicability [Электронный ресурс] / W. Weibull. URL: https://pdfs.semanticscholar.org/88c3/7770028e7ed61180a34d6a837a9a4db 3b264.pdf (дата обращения: 21.12.2024).

- 23. ГОСТ Р МЭК 61078-2021. Надежность в технике. Структурная схема надежности (переиздание). (Введ. 01.01.2022 взамен ГОСТ Р 51901.14-2007). М.: Стандартинформ, 2021. 94 с.

- 24. Microwind & Dsch Version 3.5 [Электронный ресурс]. URL: https://www.yumpu.com/en/document/view/40386405/microwind-manual-lite-v35pdf-moodle (дата обращения: 12.12.2024).

- 25. Тюрин, С.Ф. Исследование операций и теория игр. Практикум: учеб. пособие / С.Ф. Тюрин. Пермь: Изд-во Перм. нац. иссл. политех. ун-та, 2017. 220 с.

- 26. Кирсанов, М.Н. Графы в Maple / М.Н. Кирсанов. М.: Физматлит, 2007. 168 с.

#### References

- 1. GOST 27.002-2015. Nadezhnost' v tekhnike Osnovnye poniatiia. Terminy i opredeleniia [GOST 27.002-2015. Reliability in engineering. Basic concepts. Terms and definitions]. Moscow: Standartinform, 2016, 23 p.

- 2. GOST 20911-89. Tekhnicheskaia diagnostika. Terminy i opredeleniia [GOST 20911-89. Technical diagnostics. Terms and definitions]. Moscow: Standartinform, 2009, 11 p.

- 3. Avduevskii V.S., Appolonov I.V., Barzilovich E.Iu. et al. Nadezhnost' i effektivnost' v tekhnike. Spravochnik v desiati tomakh [Reliability and efficiency in engineering. Handbook in ten volumes]. V.S. Avduevskii (editor). *Reliability and efficiency in engineering*. *Handbook in 10 volumes*. (In Russian), 1990, vol. 1-10, 3092 p.

- 4. Stuck-At Fault, available at: https://web.stanford.edu/class/ee386/public/stuck\_at\_fault\_6per\_page.pdf (accessed 21 December 2024).

- 5. DFT Tutorial, Part 1, available at: https://www.eecg.utoronto.ca/~ece1767/notes/lect2.pdf (accessed 21 December 2024).

- 6. Maksimenko S.L., Melekhin V.F., Filippov A.S. Analiz problemy postroeniia radiatsionno-stoikikh informatsionno-upravliaiushchikh sistem [Analysis of the problem of constructing radiation-resistant information and control systems]. *Informatsionno-upravliaiushchie sistemy*, 2012, no. 2 (57), pp. 18-25.

- 7. Error detection or correction of the data by redundancy in hardware (epo) patents (Class 714/E11.054), available at: https://patents.justia.com/patents-by-us-classification/714/E11.054 (accessed 12 January 2021).

- 8. Carmichael C. Triple module redundancy design techniques for virtex FPGAs, available at: https://www.xilinx.com/support/documentation/application\_notes/xapp197.pdf (accessed 12 January 2021).

- 9. Tyurin S.F. Quadding against tripling & deep tripling. *Journal of Applied Mathematics and Computation*, 2018. DOI: 10.26855/jamc.2018.06.001

- 10. Tyurin S.A., Vikhorev R.V. A Decoder Look up tables for FPGAs. *International Journal of Computing*, 2021, vol. 20, iss. 3, pp. 365-373. DOI: 10.47839/ijc.20.3.2282

- 11. Tyurin S.F. Retention of functional completeness of Boolean functions under "failures" of the arguments. *Automation and Remote Control*, 1999, vol. 60, no. 9, part 2, pp. 1360-1367.

- 12. Transistor-level defect tolerant digital system design at the nanoscale, available at: https://www.researchgate.net/publication/237273805\_Transistor-Level\_Defect\_Tolerant\_Digital\_System\_Design\_at\_the \_Nanoscale (accessed 12 December 2024).

- 13. El-Maleh Aiman H., Al-Yamani Ahmad, Al-Hashimi Bashir M. Transistor-Level Defect Tolerant Digital System Design at the Nanoscale, available at: https://www.researchgate.net/publication/237273805\_Transistor-Level\_Defect\_Tolerant\_Digital\_System\_Design\_at\_the\_Nanoscale (accessed 23 December 2024).

- 14. Tyurin S.F. Hyper redundancy for super reliable FPGAs. *Radioelectronic and computer systems*, 2021, no. 1, pp. 119-132, available at: http://nti.khai.edu/ojs/index.php/reks/article/view/reks.2021.1.11/1449 (accessed 04 July 2024).

- 15. Nikitin M.S., Tiurin S.F. Topologicheskie osobennosti tranzistornogo rezervirovaniia elementov PLIS [Topological features of transistor redundancy of FPGA elements]. *Nanoindustriia*, 2022, vol. 15, no. S8-1 (113), pp. 160-163.

- 16. Tyurin S., Kamenskih A. Green logic: models, methods, algorithms. *Green IT Engineering: Concepts, Models, Complex Systems Architectures*. Eds. Kharchenko Vyacheslav, Kondratenko Yuriy, Kacprzyk Janusz, 2016, pp. 69-86. DOI: 10.1007/978-3-319-44162-7

- 17. Tyurin S. Green Logic: Green LUT FPGA Concepts, Models and Evaluations. *Green IT Engineering: Concepts, Models, Complex Systems Architectures, Studies in Systems, Decision and Control*, V. Kharchenko, Y. Kondratenko, J. Kacprzyk (Eds.). XIV, 355 p. 147 illus. Berlin, Heidelberg: Springer International Publishing, 2017. P. 241–261. DOI: 10.1007/978-3-319-44162-7\_4

- 18. Mead C.A., Conway L. Introduction to VLSI Systems, available at: https://www.researchgate.net/publication/234388249\_Introduction\_to\_VLSI\_s ystems (accessed 12 July 2023).

- 19. Tyurin, S.F. LUT's Sliding Backup / S.F. Tyurin // IEEE transactions on device and materials reliability. March 2019. Vol. 19, iss. 1. P. 221–225. DOI: 10.1109/TDMR.2019.2898724

- 20. Tyurin S. A Quad CMOS gates checking method. *International Journal of Computing*, 2019, vol. 18, iss. 3, pp. 258-264,

- 21. Tyurin S.F. Investigation of a hybrid redundancy in the faulttolerant systems. *Radio electronics computer science control*, 2019, iss. 2. pp.15-22. DOI: 10.15588/1607-3274-2019-2-3

- 22. Weibull W.A Statistical distribution function of wide applicability, available at: https://pdfs.semanticscholar.org/88c3/7770028e7ed61180a34d6 a837a9a4db3b264.pdf (accessed 21 December 2024).

- 23. GOST R MEK 61078-2021 Nadezhnost' v tekhnike. Strukturnaia skhema nadezhnosti (pereizdanie). (Vved. 01.01.2022 vzamen GOST R 51901.14-2007) [GOST R IEC 61078-2021 Reliability in engineering. Structural diagram of reliability (reissue). (Introduced 01.01.2022 to replace GOST R 51901.14-2007)]. Moscow: Standartinform, 2021, 94 p.

- 24. Microwind & Dsch Version 3.5, available at: https://www.yumpu.com/en/document/view/40386405/microwind-manual-lite-v35pdf-moodle (accessed 12 December 2024).

- 25. Tiurin C.F. Issledovanie operatsii i teoriia igr. Praktikum [Operations research and game theory. Practicum]. Perm': Permskii natsional'nyi issledovatel'skii politekhnicheskii universitet, 2017, 220 p.

- 26. Kirsanov M.N. Grafy v Maple [Graphs in Maple]. Moscow: Fizmatlit, 2007, 168 p., pp. 151-154.

#### Сведения об авторе

**Никитин Максим Сергеевич** (Пермь, Российская Федерация) — аспирант кафедры «Автоматика и телемеханика» Пермского национального исследовательского политехнического университета (614099, Пермь, Комсомольский пр., 29, e-mail: mann1k@yandex.ru).

#### **About the authors**

**Maxim S. Nikitin** (Perm, Russian Federation) – Graduate Student of the Department of Automation and Telemechanic Perm National Research Polytechnic University (614099, Perm, 29, Komsomolsky, pr., e-mail: mann1k@yandex.ru).

Поступила: 21.05.2025. Одобрена: 27.05.2025. Принята к публикации: 01.06.2025.

Финансирование. Исследование не имело спонсорской поддержки.

**Конфликт интересов.** Автор заявляет об отсутствии конфликта интересов по отношению к статье.

Вклад автора. 100 %.

Просьба ссылаться на эту статью в русскоязычных источниках следующим образом: Никитин, М.С. Алгоритм синтеза транзисторной схемы с многовариантным резервированием / М.С. Никитин // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. — 2025. — № 54. — С. 267—281. DOI: 10.15593/2224-9397/2025.1.12

Please cite this article in English as:

Nikitin M.S. Multi-optional redundancy transistor circuit design algorithm. *Perm National Research Polytechnic University Bulletin. Electrotechnics, information technologies, control systems*, 2025, no. 54, pp. 267-281. DOI: 10.15593/2224-9397/2025.1.12