2025 Электротехника, информационные технологии, системы управления

№ 53

Научная статья

DOI: 10.15593/2224-9397/2025.1.08

УДК 004.89

### И.А. Васенин

Пермский национальный исследовательский политехнический университет, Пермь, Российская Федерация

# МОДЕЛИРОВАНИЕ ЭЛЕМЕНТОВ ПЛИС, ИСПОЛЬЗУЮЩИХ КОМБИНИРОВАННОЕ КОДИРОВАНИЕ

Совершенствование характеристик программируемых логических интегральных схем (ПЛИС), несмотря на достигнутые за более чем 40 лет их развития впечатляющие показатели по количеству транзисторов (десятки миллиардов), логических и других элементов в одной микросхеме, является актуальной задачей. Прежде всего это относится к быстродействию, которое уступает заказным схемам ASIC (Application-Specific Integrated Circuit) и полузаказным схемам (базовые матричные кристаллы – БМК, ULA – Uncommitted Logic Array). Однако последние разработки передовых производителей позволяют предположить, что значительное увеличение количества элементов (десятки миллионов) и числа переменных (до восьми) реализуемых ими функций позволят вскоре выполнять вычисления по принципу «Логики не жалеть!», который был не мыслим еще недавно, в начале «цифрового тысячелетия». В этом случае получается, что необходим минимум один транзистор от ячейки конфигурационной памяти, хранящей значение функции в совершенной дизъюнктивной нормальной форме (СДНФ), до триггера результата без учета инверторов-восстановителей логического уровня сигнала, что требует так называемого унитарного кода и 2n связей вместо n для известного элемента LUT (Look Up Table), где n – количество переменных. Такой способ используется в существующих коммутаторах связей (мультиплексорах маршрутизации - Routing Multiplexers). Экспоненциально возрастающее число линий связи или ячеек памяти может достигать неприемлемых значений, и тогда целесообразно несколько уменьшить его введением комбинированных вариантов кодирования. В статье рассматривается моделирование топологии вариантов ранее предложенного и запатентованного элемента с комбинированным кодированием как для вычисления логических функций. так и для коммутации связей ПЛИС. Целью исследования является моделирование топологии нового предложенного элемента ПЛИС, использующего комбинированное кодирование переменных логической функции или настроечной информации для коммутации связей. Методы исследования базируются на научно-методическом аппарате схемотехнического и топологического моделирования в системах National Instruments. Multisim и Microwind & Dsch Version 3.5. В результате исследования получены топологии предложенных элементов, их сравнительные характеристики с существующими по временной задержке, занимаемой площади кристалла микросхемы и количеству транзисторов, а также потребляемой мощности. Практическая значимость: разработанные схемы электрические функциональные и топология элементов с комбинированным кодированием позволяют разработчикам усовершенствовать архитектуру ПЛИС по показателям быстродействия вычисления логических функций и/или объема конфигурационной памяти коммутаций.

**Ключевые слова:** логическая функция, маршрутизатор связей, ПЛИС, LUT, унитарный код, топология.

### I.A. Vasenin

Perm National Research Polytechnic University, Perm, Russian Federation

### SIMULATION OF FPGA ELEMENTS USING COMBINED CODING

Improving the characteristics of programmable logic integrated circuits (FPGAs), despite the impressive figures achieved over more than 40 years of their development in terms of the number of transistors (tens of billions), logic gates and other elements in a single chip, is an urgent task. First of all, this applies to the speed, which is inferior to custom ASIC (Application-Specific Integrated Circuit) circuits and semi-custom circuits (ULA - Uncommitted Logic Array). However, the latest developments of leading manufacturers allow us to assume that a significant increase in the number of elements (tens of millions) and the number of variables (up to eight) of the functions they implement will soon make it possible to perform calculations according to the principle of "Do not spare logic!", which was unthinkable just recently, at the beginning of the "digital millennium". In this case, it turns out that at least one transistor is required from the configuration memory cell storing the function value in perfect disjunctive normal form (PDNF) to the result flip-flop without taking into account the inverters-restorers of the logical signal level, which requires the so-called One-Hot (One-Cold) encoding and 2n connections instead of n for the well-known LUT (Look Up Table) gate, where n is the number of variables. This method is used in existing communication switches (routing multiplexers). The exponentially increasing number of communication lines or memory cells can reach unacceptable values, and then it is advisable to reduce it somewhat by introducing combined encoding options. The article considers lay-out simulation of the previously proposed and patented gate with combined encoding both for calculating logical functions and for switching FPGA connections. The aim of the study is the lay-out simulation of the new proposed FPGA element, which uses combined coding of the variables of the logical function or configuration information for the routing multiplexers. The research methods are based on the scientific and methodological apparatus of circuit and lay-out simulation in the National Instruments systems. Multisim and Microwind & Dsch Version 3.5. As a result of the study, the topologies of the proposed elements, their comparative characteristics with existing ones in terms of time delay, occupied area of the microcircuit crystal and the number of transistors, as well as power consumption were obtained. Discussion: designed electrical functional circuits and topology of elements with combined coding allow developers to improve the FPGA architecture in terms of the performance of calculating logical functions and/or the volume of configuration switching memory.

Keywords: Logic Functions, Routing Multiplexers. FPGA, LUT, One-Hot Coding, Lay-Out.

### Ввеление

Наиболее детальное описание программируемых логических интегральных схем (ПЛИС) для русскоязычных исследователей, на взгляд автора, имеется в работах профессора А.В. Строгонова из Воронежского государственного технического университета [1–6]. В работе [1] в соавторстве с С.А. Цыбиным, являющимся генеральным директором Воронежского КТЦ «Электроника» (АО «Конструкторскотехнологический центр «Электроника»), одним из немногих предприятий по выпуску ПЛИС в РФ, приведено кроме прочего описание схем электрических функциональных логического элемента LUT (Look Up

Тable) и коммутатора связей (мультиплексора маршрутизации – Routing Multiplexers). В частности, описан вариант двухступенчатого унитарного кодирования в коммутаторе связей с целью сокращения объема памяти конфигураций. Дальнейшее развитие такого варианта возможно путем соединения в одном устройстве LUT (Look Up Table) и Routing Multiplexers (RM) как для маршрутизации, так и для ускоренного вычисления логических функций. Это привело к разработке элемента с комбинированным кодированием [7, 8]. Использование такого элемента совместно с другими инновационными решениями, полученными в исследовательской группе кафедры «Автоматика и телемеханика» ПНИПУ [9–13], позволяет получить новые, перспективные вычислительные архитектуры [14]. Это способствует расширению области применения ПЛИС [15–20].

Однако разработка топологических моделей новых решений [21–24] имеет свои особенности и в настоящее время наталкивается на серьёзные известные ограничения.

Тем не менее проведенные автором исследования схемотехнических и топологических моделей в доступных САПР [25, 26] подтвердили работоспособность разработанных технических решений, но сравнительные характеристики не полностью соответствовали теоретическим положениям. В ранних работах топологическое моделирование выполнялось в системах, качество которых вызывало определенные сомнения, не было описано в полной мере, что затрудняло разработчикам возможность создавать архитектуры перспективных ПЛИС.

Автору удалось организовать переписку с индийскими учёными и получить от разработчиков Microwind лицензионную версию для обучения (на несколько месяцев с правилами CMOS только, к сожалению, не ниже 32 nm) и выполнить необходимые эксперименты по исследованию моделей предложенных элементов на топологическом уровне и получить достоверные сравнительные характеристики с характеристиками известных элементов.

Целью представленной работы является описание проведенного моделирования топологий на лицензионном ПО для учебных целей нового предложенного элемента ПЛИС, использующего комбинированное кодирование переменных логической функции или настроечной информации для коммутации связей.

### 1. Разработка элемента на одну переменную

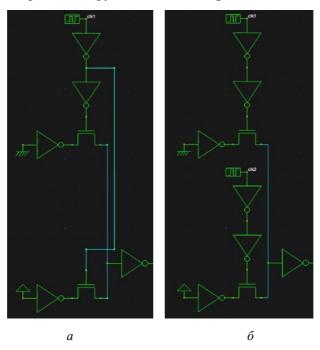

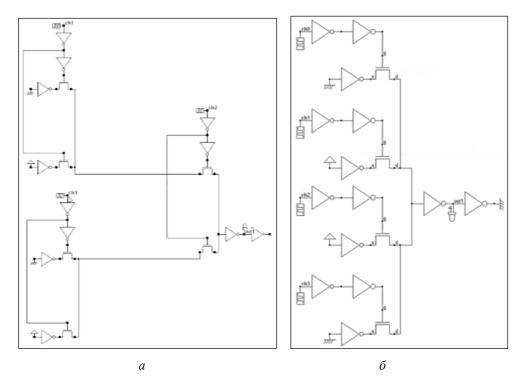

Элемент 1-LUT реализует функцию одной переменной. Будем называть коммутатор на две связи, используемый для вычисления функции, также1-LUT, но унитарным. В начале в Microwind [26] строится схема электрическая функциональная (рис. 1).

Рис. 1. Схема электрическая функциональная 1-LUT, настроенная на реализацию логической функции инверсии входного сигнала Clk: a — известного;  $\delta$  — унитарного

Дерево транзисторов строится из двух n-MOП (n-MOS) транзисторов; инверторы предполагают использование каждого из КМОП транзисторов (n-MOS, p-MOS: Complementary MOS, CMOS).

Эти схемы соответствующих элементов (см. рис. 1) могут быть использованы не для вычисления логической функции, а для коммутации связей (мультиплексора 2-1) (рис. 2).

Демультиплексор 1-2 строится так, как показано на рис. 3.

Далее был получен соответствующий VHDL (Very high speed integrated circuits) Hardware Description Language), и по нему строилась топология CMOS 32 nm, например, для схемы на рис. 1–4.

Рис. 2. Схема электрическая функциональная коммутатора связей — мультиплексора 2-1: a — на основе1-LUT позиционного;  $\sigma$  — на основе1-LUT унитарного

Рис. 3. Схема электрическая функциональная коммутатора связей — демультиплексора 2-1: a — на основе1-LUT позиционного;  $\delta$  — на основе1-LUT унитарного

a

б

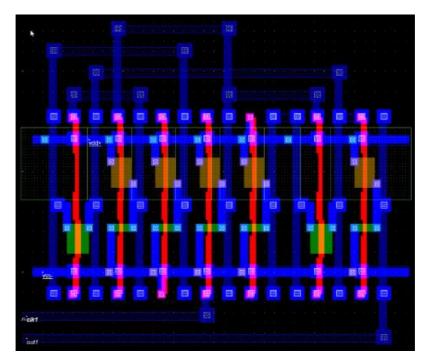

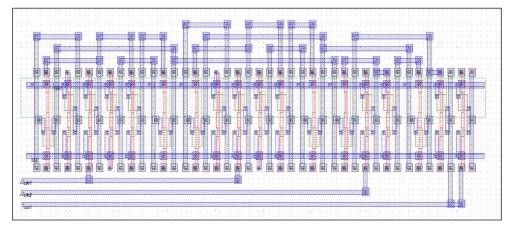

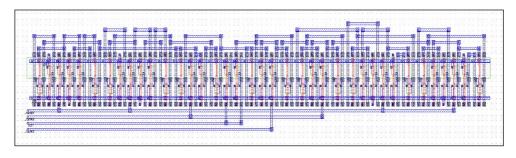

Рис. 4. Топология 1-LUT: a — известного (позиционного);  $\delta$  — унитарного

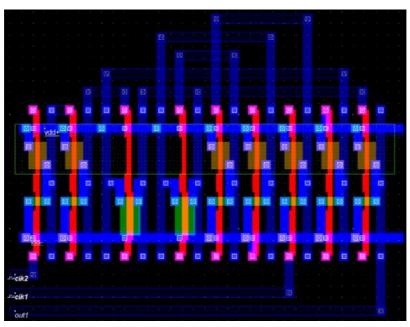

В дальнейшем для топологий, приведенных на рис. 4, выполнялось временное моделирование с получением осциллограмм (рис. 5).

Рис. 5. Временная диаграмма работы: a — существующего 1-LUT CMOS 32 nm;  $\delta$  — унитарного 1-LUT CMOS 32 nm

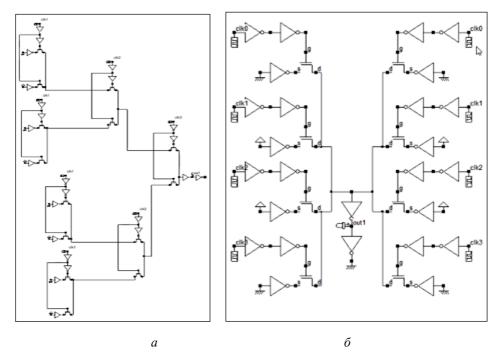

Рис. 6. Схема электрическая функциональная 2-LUT, настроенная на реализацию логической функции инверсии входного сигнала Clk1- Clk2: a — известного;  $\delta$  — унитарного

Как видно по графикам временных диаграмм, что и по форме сигнала, и по временным параметрам унитарный вариант несколько лучше существующего, но у существующего одна линия переменной, а у унитарного две, и нужно еще да дополнительных инвертора, хотя по конфигурационной памяти функции они одинаковы.

# 2. Разработка элемента на две переменных

Построенные схемы электрические функциональные 2-LUT, настроенные на реализацию логической функции инверсии входного сигнала, показаны на рис. 6.

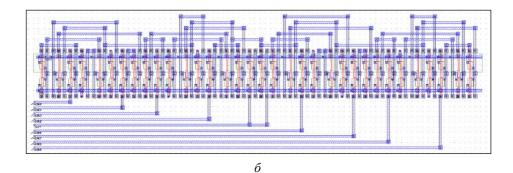

Полученные соответствующие топологии показаны на рис. 7.

а

6

Рис. 7. Топологии 2-LUT: a – известного (позиционного);  $\delta$  – унитарного

При построении графиков временных диаграмм можно увидеть, что сигнал не доходит до 0. Такой эффект наблюдается при моделировании схем от 2 переменных. Известно, что для схемы 2-LUT уже требуется восстановитель логического уровня сигнала.

# 3. Разработка элемента на три переменных

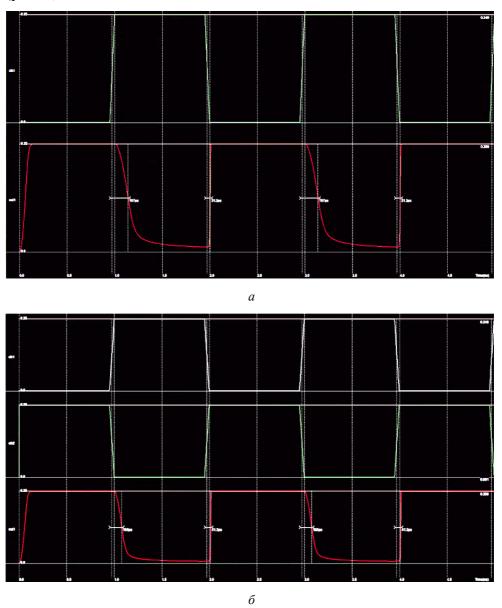

Построенные схемы электрические функциональные 2-LUT, настроенные на реализацию логической функции инверсии входного сигнала, показаны на рис. 9.

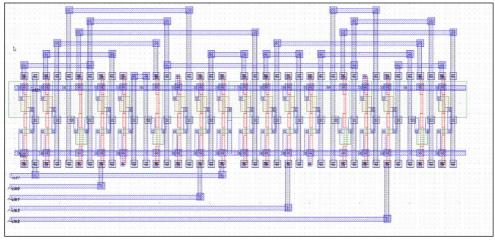

Рис. 9. Схемы электрические функциональные 3-LUT: a – известного (позиционного);  $\delta$  – унитарного

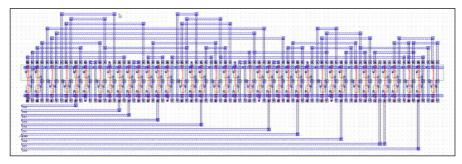

Полученные соответствующие топологии показаны на рис. 10.

# 4. Разработка комбинированного элемента

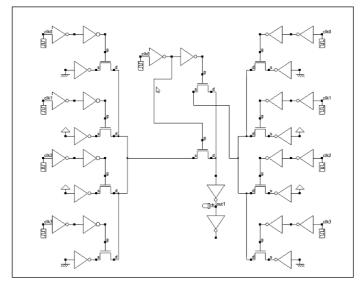

Предлагаемый комбинированный вариант имеет позиционную часть (1-LUT) и унитарную, включающую два унитарных 2-LUT (рис. 11).

Рис. 10. Топологии 3-LUT: a — известного (позиционного);  $\delta$  — унитарного

Рис. 10. Окончание

Рис. 11. Схема электрическая функциональная предлагаемого комбинированного 3-LUT

Топология предлагаемого комбинированного 3-LUT представлена на рис. 12.

Рис. 12. Топология предлагаемого комбинированного 3-LUT

## 5. Сравнение полученных показателей

В процессе моделирования кроме временной задержки оценивались показатели площади кристалла, потребляемой мощности и количества транзисторов. Сравнение полученных показателей разработанных топологий при напряжении 0,35 В и частоте 0,5 ГГц показано в таблице.

|                  |                        | ~ ن            | U                  |

|------------------|------------------------|----------------|--------------------|

| Грарпение поп    | VIDAUULIV HAKADA       | ταπαμ ησοησήστ | анных топологий    |

| C pablicline non | . y TCIIIIDIA IIUKasa. | ichen paspaooi | annibia ionomonini |

|                  |                        |                |                    |

| №<br>п/<br>п | Название                      | Временная<br>задержка<br>(Propagation<br>delay) по<br>фронту (plh)<br>ps | Временная<br>задержка<br>(Propagation<br>Delay) по<br>срезу (phl) ps | Пло-<br>щадь<br>кри-<br>сталла<br>nm^2 | Потребля-<br>емая<br>мощность<br>microWatt | Число линий связи для пере-менных/ число конфигурационных бит для сигналов связи |

|--------------|-------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------|

| 1            | позицЛУТ-1                    | 31,3                                                                     | 167                                                                  | 12,5                                   | 0,567                                      | 1                                                                                |

| 2            | унитЛУТ-1                     | 41,3                                                                     | 105                                                                  | 9,6                                    | 0,552                                      | 2                                                                                |

| 3            | позицЛУТ-2                    | 54,6                                                                     | 485                                                                  | 33                                     | 1,367                                      | 2                                                                                |

| 4            | унитЛУТ-2                     | 55.4                                                                     | 300                                                                  | 39,6                                   | 5,924                                      | 4                                                                                |

| 5            | позицЛУТ-3                    | 62,1                                                                     | 911                                                                  | 78,2                                   | 2,245                                      | 3                                                                                |

| 6            | унитЛУТ-3                     | 50,7                                                                     | 354                                                                  | 88,8                                   | 1,833                                      | 8                                                                                |

| 7            | Комбиниро-<br>ванный<br>ЛУТ-3 | 62,1                                                                     | 507                                                                  | 121,5                                  | 1,980                                      | 5                                                                                |

Таким образом, предлагаемый комбинированный элемент выигрывает по числу линий связи у унитарного и обладает меньшей временной задержкой, чем позиционный.

Из полученных результатов видно, что унитарный элемент (на 1, 2, 3 переменные) имеют меньшую временную задержку, как и следует из теории.

### Заключение

Выполненное моделирование подтвердило работоспособность унитарных и комбинированных элементов при вычислении заданной логической функции. Унитарные элементы обладают меньшей временной задержкой, чем позиционные, однако по количеству линий связи, площади кристалла и объему конфигурационной памяти коммутаций они значительно проигрывают. Промежуточный вариант с комбинированным кодированием показал теоретически предсказанные результаты: по числу линий связи/ числу конфигурационных бит он об-

ладает средними показателями, выигрывая у позиционного элемента по временной задержке. Для трех переменных выигрыш в быстродействии относительно позиционного составляет порядка 79 %, а проигрыш относительно полностью унитарного порядка — 43 %. Выигрыш по числу линий связи (объему памяти) относительно унитарного составляет 60 %, проигрыш относительно позиционного — 66 %. Целесообразно использовать разработанные топологии при проектировании архитектур новых перспективных ПЛИС. В дальнейшем необходимо уточнить полученные оценки для более современных технологий и с учетом восстановителей логического уровня сигналов для большей размерности с учетом ограничений Мида–Конвей [27].

## Библиографический список

- 1. Строгонов, А.В. Программируемая коммутация ПЛИС: взгляд изнутри [Электронный ресурс] / А.В. Строгонов, С.А. Цыбин. URL: http://www.kit-e.ru/articles/plis/2010\_11\_56.php (дата обращения: 17.06.2024).

- 2. Строгонов, А. Современные тенденции развития ПЛИС: от системной интеграции к искусственному интеллекту / А. Строгонов, П. Городков // Электроника: Наука, технология, бизнес. 2020. 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100

- 3. Строгонов, А. Обзор программных средств с открытым исходным кодом для исследования современных архитектур ПЛИС XILINX / А. Строгонов, М. Кривчун, П. Городков // Электроника: Наука, технология, бизнес. -2020. -№ 1 (192). C. 100–107.

- 4. Арбузов, И. Пример разработки проекта в базисе ПЛИС 5578ТС024 / И. Арбузов, А. Строгонов, П. Городков // Компоненты и технологии. -2019. -№ 7 (216). C. 66–69.

- 5. Строгонов, А. Обзор ПЛИС китайских производителей [Электронный ресурс] / А. Строгонов, П. Городков. URL: https://www.elibrary.ru/download/elibrary\_48565021\_33092934.pdf (дата обращения: 17.11.2023).

- 6. Строгонов, А. Проектирование конечных автоматов в приложении STATEFLOW системы MatLab / Simulink с последующей реализацией в базисе ПЛИС / А. Строгонов // Электроника: Наука, технология, бизнес. -2023. -№ 3 (224). C. 134–147.

- 7. Тюрин, С.Ф. Логические элементы ПЛИС FPGA на основе комбинированного кодирования переменных / С.Ф. Тюрин, И.А. Васенин, С.И. Советов // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. 2023. № 46. С. 83–107. DOI: 10.15593/2224-9397/2023.2.04

- 8. Программируемое логическое устройство: пат. Рос. Федерация / Тюрин С.Ф., Васенин И.А., Степченков Ю.А., Дьяченко Ю.Г., Советов С.И. 2811404; заявл. 02.08.2023; опубл. 11.01.2024

- 9. Новый подход к реализации логических функций в ПЛИС / С.Ф. Тюрин, С.И. Советов, Ю.А. Степченков, Ю.Г. Дьяченко // Системы и средства информатики. 2024. Т. 34, № 4. С. 3–15. DOI: 10.14357/08696527240401

- 10. Новая концепция ПЛИС с выбором режима работы и двухрежимный базисный логический элемент / И.А. Соколов, С.Ф. Тюрин, Ю.А. Степченков, Ю.Г. Дьяченко, М.С. Никитин, С.И. Советов // Системы высокой доступности. -2024. Т. 20, № 2. С. 56–64. DOI: 10.14357/08696527240401

- 11. Тюрин, С.Ф. Логический элемент ПЛИС FPGA, реализующий функцию и дешифрацию набора переменных / С.Ф. Тюрин, С.И. Советов // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. − 2023. − № 47. − С. 5–31. DOI: 10.15593/2224-9397/2023.3.01

- 12. Советов, С.И. Разработка топологии многофункционального логического элемента плис / С.И. Советов // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. − 2023. № 48. C. 30–49. DOI: 10.15593/2224-9397/2023.4.02

- 13. Тюрин, С.Ф. Логический элемент программируемых логических интегральных схем FPGA, вычисляющий функцию одновременно с дешифрацией входных переменных / С.Ф. Тюрин, С.И. Советов // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. 2024. № 50. С. 216–234. DOI: 10.15593/2224-9397/2024.2.11

- 14. Развитие гибридной многоядерной рекуррентной архитектуры на ПЛИС / Ю.А. Степченков, Н.В. Морозов, Ю.Г. Дьяченко, Д.В. Хилько, Д.Ю. Степченков // Системы и средства информатики. -2020. T. 30, № 4. C. 95–101.

- 15. Development of a device for multiplying numbers by means of FPGA / N.M. Berezin, I.E. Chernetskaya, V.S. Panishchev, A.M. Shabarov // Published under licence by IOP Publishing Ltd. Journal of Physics: Conference Series. Vol. 2142, XI International Conference on High-performance computing systems and technologies in scientific research, automation of control and production (HPCST 2021); 21–22 May 2021. Barnaul, Russia. DOI: 10.1088/1742-6596/2142/1/012001

- 16. Методика проектирования преобразователя кода Грея на ПЛИС / А.А. Пирогов, Ю.А. Пирогова, А.В. Башкиров, М.Ю. Чепелев, Б.И. Жилин // Вестник Воронеж. института ФСИН России. 2020. № 3. С. 9—14.

- 17. Enhancing blockchain security and efficiency through FPGA-based consensus mechanisms and post-quantum cryptography / Jalel Ktari, Tarek Frikha, Tarek Frikha, Monia Hamdi, Habib Hamam. May 2024. DOI: 10.2174/0123520965288815240424054237

- 18. FPGA accelerated post-quantum cryptography / He Li, Yongming Tang, Zhiqiang Que, Jiliang Zhang // IEEE Transactions on Nanotechnolog. January 2022. 99. P. 1–7. DOI: 10.1109/TNANO.2022.3217802

- 19. Levental, Maksim. Tensor networks for simulating quantum circuits on FPGAs [Электронный ресурс] / Maksim Levental. August 2021. URL: https://www.researchgate.net/publication/353941749\_Tensor\_Networks\_for\_Si mulating Quantum Circuits on FPGAs (дата обращения: 17.11.2023).

- 20. Hemin, Rahimi. Optimum implementation of digital logic circuits on 3D FPGAs / Hemin Rahimi // Thesis for: MasterAdvisor: Dr. Hadi jahanirad. November 2023. DOI: 10.13140/RG.2.2.24347.85283

- 21. Monther, Abusultan. A comparison of FinFET based FPGA LUT / Monther Abusultan, Sunil P. Khatri // Texas A&M University, College Station, TX, USA. Published in ACM Great Lakes Symposium on VLSI, 2014. DOI: 10.1145/2591513.2591596

- 22. Vikhorev, R. Universal logic cells to implement systems functions / R. Vikhorev // Conference of Russian Young Researchers in Electri-

- cal and Electronic Engineering. IEEE, 2016. P. 404–406. DOI: 10.1109/EIConRusNW.2016.7448197

- 23. Vikhorev, R. Improved FPGA logic elements and their simulation / R. Vikhorev // Conference of Russian Young Researchers in Electrical and Electronic Engineering. IEEE, 2018. P. 275–280. DOI: 10.1109/EIConRus.2018.8317080

- 24. Skornyakova, A.Yu. Self-Timed LUT Layout Simulation / A.Yu. Skornyakova, R.V. Vikhorev // Conference of Russian Young Researchers in Electrical and Electronic Engineering. IEEE, 2020. P. 176–179. DOI: 10.1109/EIConRus49466.2020.9039374

- 25. National Instruments. Multisim [Электронный ресурс]. URL: http://www.ni.com/multisim/ (дата обращения: 17.11.2023).

- 26. Microwind & Dsch Version 3.5 [Электронный ресурс]. URL: https://www.yumpu.com/en/document/view/40386405/microwind-manual-lite-v35pdf-moodle (дата обращения: 21.12.2024).

- 27. Mead, C.A. Introduction to VLSI Systems [Электронный ресурс] / C.A. Mead, L. Conway. URL: https://www.researchgate.net/publication/234388249\_Introduction\_to\_VLSI\_systems (дата обращения: 12.07.2023).

### References

- 1. Strogonov A.V., Tsybin S.A. Programmiruemaia kommutatsiia PLIS: vzgliad iznutri [Programmable switching FPGA: an inside look], available at: http://www.kit-e.ru/articles/plis/2010\_11\_56.php (accessed 17 June 2024).

- 2. Strogonov A., Gorodkov P. Sovremennye tendentsii razvitiia PLIS: ot sistemnoi integratsii k iskusstvennomu intellektu [Modern trends in the development of FPGAs: from system integration to artificial intelligence]. *Elektronika: Nauka, tekhnologiia, biznes*, 2020, no. 4 (195), pp. 46-56.

- 3. Strogonov A., Krivchun M., Gorodkov P. Obzor programmnykh sredstv s otkrytym iskhodnym kodom dlia issledovaniia sovremennykh arkhitektur PLIS XILINX [Design of finite state machines in the STATEFLOW application of the MatLab Simulink system with subsequent implementation in the FPGA basis]. *Elektronika: Nauka, tekhnologiia, biznes*, 2020, no. 1 (192), pp. 100-107.

- 4. Arbuzov I., Strogonov A., Gorodkov P. Primer razrabotki proekta v bazise PLIS 5578TS024 [Review of open source software tools for researching modern FPGA architectures XILINX]. *Komponenty i tekhnologii*, 2019, no. 7 (216), pp. 66-69.

- 5. Strogonov A., Gorodkov P. Obzor PLIS kitaiskikh proizvoditelei [An example of project development based on FPGA 5578TS024], available at: https://www.elibrary.ru/download/elibrary\_48565021\_33092934.pdf (accessed 17 November 2023).

- 6. Strogonov A. Proektirovanie konechnykh avtomatov v prilozhenii STATEFLOW sistemy MatLab Simulink s posleduiushchei realizatsiei v bazise PLIS [Review of FPGAs from Chinese manufacturers]. *Elektronika: Nauka, tekhnologiia, biznes*, 2023, no. 3 (224), pp. 134-147.

- 7. Tiurin S.F., Vasenin I.A., Sovetov S.I. Logicheskie elementy PLIS FPGA na osnove kombinirovannogo kodirovaniia peremennykh [FPGA gates using combined variables coding]. *Vestnik Permskogo natsional'nogo issledovatel'skogo politekhnicheskogo universiteta. Elektrotekhnika, informatsionnye tekhnologii, sistemy upravleniia*, 2023, no. 46, pp. 83-107. DOI: 10.15593/2224-9397/2023.2.04

- 8. Tiurin S.F., Vasenin I.A., Stepchenkov Iu.A., D'iachenko Iu.G., Sovetov S.I. Programmiruemoe logicheskoe ustroistvo [Programmable logic device]. Patent Rossiiskaia Federatsiia no. 2811404 (2024).

- 9. Tiurin S.F., Sovetov S.I., Stepchenkov Iu.A., D'iachenko Iu.G. Novyi podkhod k realizatsii logicheskikh funktsii v PLIS [A New Approach to Implementing Logical Functions in FPGAs]. *Sistemy i sredstva informatiki*, 2024, vol. 34, no. 4, pp. 3-15. DOI: 10.14357/08696527240401

- 10. Sokolov I.A., Tiurin S.F., Stepchenkov Iu.A., D'iachenko Iu.G., Nikitin M.S., Sovetov S.I. Novaia kontseptsiia PLIS s vyborom rezhima raboty i dvukhrezhimnyi bazisnyi logicheskii element [Novel FPGA clock concept and dual-mode basic logic gate]. *Sistemy vysokoi dostupnosti*, 2024, vol. 20, no. 2, pp. 56-64. DOI: 10.14357/08696527240401

- 11. Tiurin S.F., Sovetov S.I. Logicheskii element PLIS FPGA, realizuiushchii funktsiiu i deshifratsiiu nabora peremennykh [FPGA LUT implementing the function and decoding of a set of variables]. *Vestnik Permskogo natsional'nogo issledovatel'skogo politekhnicheskogo universiteta. Elektrotekhnika, informatsionnye tekhnologii, sistemy upravleniia*, 2023, no. 47, pp. 5-31. DOI: 10.15593/2224-9397/2023.3.01

- S.I. topologii 12. Sovetov Razrabotka mnogofunktsional'nogo logicheskogo elementa PLIS [Lay-out development of multifunctional logic element for FPGA]. Vestnik Permskogo natsional'nogo issledovatel'skogo politekhnicheskogo universiteta. Elektrotekhnika, informatsionnye tekhnologii, sistemy upravleniia, 2023, no. 48, pp. 30-49. DOI: 10.15593/2224-9397/2023.4.02

- 13. Tiurin S.F., Sovetov S.I. Logicheskii element programmiruemykh logicheskikh integral'nykh skhem FPGA, vychisliaiushchii funktsiiu odnovremenno s deshifratsiei vkhodnykh peremennykh [FPGA logic element that calculates a function simultaneously with decoding input variables]. *Vestnik Permskogo natsional'nogo issledovatel'skogo politekhnicheskogo universiteta. Elektrotekhnika, informatsionnye tekhnologii, sistemy upravleniia*, 2024, no. 50, pp. 216-234. DOI: 10.15593/2224-9397/2024.2.11

- 14. Stepchenkov Iu.A., Morozov N.V., D'iachenko Iu.G., Khil'ko D.V., Stepchenkov D.Iu. Razvitie gibridnoi mnogoiadernoi rekurrentnoi arkhitektury na PLIS [Development of a hybrid multi-core recurrent architecture on FPGA]. *Sistemy i sredstva informatiki*, 2020, vol. 30, no. 4, pp. 95-101.

- 15. Berezin N.M., Chernetskaya I.E., Panishchev V.S., Shabarov A.M. Development of a device for multiplying numbers by means of FPGA. *Published under licence by IOP Publishing Ltd. Journal of Physics: Conference Series. Vol. 2142, XI International Conference on High-performance computing systems and technologies in scientific research, automation of control and production (HPCST 2021); 21-22 May 2021.* Barnaul, Russia. DOI: 10.1088/1742-6596/2142/1/012001

- 16. Pirogov A.A., Pirogova Iu.A., Bashkirov A.V., Chepelev M.Iu., Zhilin B.I. Metodika proektirovaniia preobrazovatelia koda Greia na PLIS [Gray Code Converter design methodology for FPGAs]. *Vestnik Voronezhskogo instituta FSIN Rossii*, 2020, no. 3, pp. 9-14.

- 17. Ktari Jalel, Frikha Tarek, Hamdi Monia, Hamam Habib. Enhancing blockchain security and efficiency through FPGA-based consensus mechanisms and post-quantum cryptography. May 2024. DOI: 10.2174/0123520965288815240424054237

- 18. Li He, Tang Yongming, Que Zhiqiang, Zhang Jiliang FPGA accelerated post-quantum cryptography. *IEEE Transactions on Nanotechnolog*. January 2022, 99, pp. 1-7. DOI: 10.1109/TNANO.2022.3217802

- 19. Levental Maksim. Tensor networks for simulating quantum circuits on FPGAs. August 2021, available at: https://www.researchgate.net/publication/353941749\_Tensor\_Networks\_for\_Simulating\_Quantum\_Circuits\_on\_FPGAs (accessed 17 November 2023).

- 20. Hemin Rahimi. Optimum implementation of digital logic circuits on 3D FPGAs. *Thesis for: MasterAdvisor: Dr. Hadi jahanirad*. November 2023. DOI: 10.13140/RG.2.2.24347.85283

- 21. Monther Abusultan, Sunil P. Khatri. A comparison of FinFET based FPGA LUT. Texas A&M University, College Station, TX, USA. Published in ACM Great Lakes Symposium on VLSI, 2014. DOI: 10.1145/2591513.2591596

- 22. Vikhorev R. Universal logic cells to implement systems functions. *Conference of Russian Young Researchers in Electrical and Electronic Engineering*. IEEE, 2016, pp. 404-406. DOI: 10.1109/EIConRusNW.2016.7448197

- 23. Vikhorev R. Improved FPGA logic elements and their simulation. *Conference of Russian Young Researchers in Electrical and Electronic Engineering*. IEEE, 2018, pp. 275-280. DOI: 10.1109/EIConRus.2018.8317080

- 24. Skornyakova A.Yu., Vikhorev R.V. Self-Timed LUT Layout Simulation. *Conference of Russian Young Researchers in Electrical and Electronic Engineering*. IEEE, 2020, pp. 176-179. DOI: 10.1109/EIConRus49466.2020.9039374

- 25. National Instruments. Multisim, available at: http://www.ni.com/multisim/ (accessed 17 November 2023).

- 26. Microwind & Dsch Version 3.5, available at: https://www.yumpu.com/en/document/view/40386405/microwind-manual-lite-v35pdf-moodle (accessed 21 December 2024).

- 27. Mead C.A., Conway L. Introduction to VLSI Systems, available at: https://www.researchgate.net/publication/234388249\_Introduction\_to\_VLSI\_s ystems (accessed 12 Juli 2023).

### Сведения об авторе

Васенин Иван Андреевич (Пермь, Российская Федерация) — аспирант кафедры «Автоматика и телемеханика» Пермского национального исследовательского политехнического университета (614990, Пермь, Комсомольский пр., 29, e-mail: Vasenin.Ioann@yandex.ru).

### About the author

**Ivan A. Vasenin** (Perm, Russian Federation) – postgraduate student of the Department of Automation and Telemechanics Perm National Research Polytechnic University (614990, Perm, 29, Komsomolsky pr., e-mail: Vasenin.Ioann@yandex.ru).

Поступила: 06.02.2025. Одобрена: 19.02.2025. Принята к публикации: 15.03.2025.

Финансирование. Исследование не имело спонсорской поддержки.

**Конфликт интересов.** Автор заявляет об отсутствии конфликта интересов по отношению к статье.

Вклад автора. 100 %.

Просьба ссылаться на эту статью в русскоязычных источниках следующим образом:

Васенин, И.А. Моделирование элементов ПЛИС, использующих комбинированное кодирование / И.А. Васенин // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. — 2025. — № 53. — С. 157–176. DOI: 10.15593/2224-9397/2025.1.08

Please cite this article in English as:

Vasenin I.A. Simulation of FPGA elements using combined coding. *Perm National Research Polytechnic University Bulletin. Electrotechnics, information technologies, control systems*, 2025, no. 53, pp. 157-176. DOI: 10.15593/2224-9397/2025.1.08